看了让人后悔晶振PCB板设计早了

来源:http://www.yijindz.com 作者:yijindz 2012年05月30

亿金电子供应晶振,石英晶振,贴片晶振,进口晶振,KDS晶振,西铁城晶振,晶振工作原理,晶振技术参数。

设计晶振时经常遇到相噪与抖动这概念,两者之间是什么关系呢?相位噪声和抖动是对同一种现象的两种不同定量方式(描述)。相位噪声是频率域的概停飞,相位噪声是用偏移频率fm处1Hz带宽内的矩形的面积,与整个功率谱曲线下包含的面积之比,单位用-dBC/Hz表示。抖动是一个时域概念,单位用pS或fS表示。

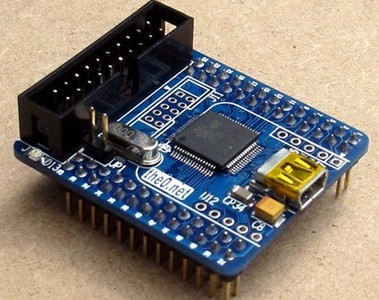

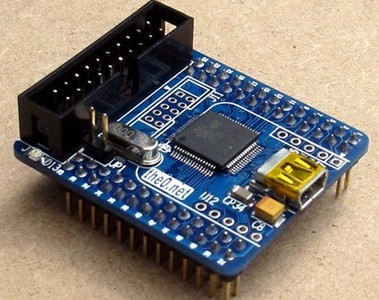

从PCB布局上考虑,晶振尽量焊在PCB上,少用插座方式,高频信号线尽可能远离敏感的模拟电路器件,数字地与模拟地由一点短接或通过外界接口相连例如插座,晶振应该设计在什么位置最好也是该考虑的要素,由于影响晶振短期稳定性的主要因素是温度变化,在设计通盘布局的考虑下,尽量避免将晶振靠近机箱外壳或靠近温度较大的部件例如风扇,还应该远离大功率射频器件例如射频功放。在振动或存在加速度变化的环境下,还应该考虑晶振的受力,确保应力分布均匀,并采取有效缓冲等减振措施。电源纹波也会对晶振产生影响,通常晶振对电源的纹波和噪声要求小于输出电压的1%,由于晶振内部有高精密电压基准,其纹波抑制,负载调整率都非常优良,精度可以达到3ppm/℃,电源系统1%以内的纹波对晶振的干扰可以忽略。

设计晶振时经常遇到相噪与抖动这概念,两者之间是什么关系呢?相位噪声和抖动是对同一种现象的两种不同定量方式(描述)。相位噪声是频率域的概停飞,相位噪声是用偏移频率fm处1Hz带宽内的矩形的面积,与整个功率谱曲线下包含的面积之比,单位用-dBC/Hz表示。抖动是一个时域概念,单位用pS或fS表示。

从PCB布局上考虑,晶振尽量焊在PCB上,少用插座方式,高频信号线尽可能远离敏感的模拟电路器件,数字地与模拟地由一点短接或通过外界接口相连例如插座,晶振应该设计在什么位置最好也是该考虑的要素,由于影响晶振短期稳定性的主要因素是温度变化,在设计通盘布局的考虑下,尽量避免将晶振靠近机箱外壳或靠近温度较大的部件例如风扇,还应该远离大功率射频器件例如射频功放。在振动或存在加速度变化的环境下,还应该考虑晶振的受力,确保应力分布均匀,并采取有效缓冲等减振措施。电源纹波也会对晶振产生影响,通常晶振对电源的纹波和噪声要求小于输出电压的1%,由于晶振内部有高精密电压基准,其纹波抑制,负载调整率都非常优良,精度可以达到3ppm/℃,电源系统1%以内的纹波对晶振的干扰可以忽略。

正在载入评论数据...

相关资讯

- [2026-02-04]Skyworks赋能Nest视频门铃开启智能家...

- [2026-02-02]瑞萨第四代R-Car汽车芯片应运而生掀起...

- [2026-01-28]电子行业新突破IQD可变供电式振荡器震...

- [2026-01-24]5G与智能时代的幕后英雄Greenray精密...

- [2026-01-21]Skyworks电子展大放送栅极驱动器与Ga...

- [2025-10-24]光刻赋能NDK晶振开启800G/1.6T光通信...

- [2025-10-18]解锁液体检测新境界美国微芯MTCH9010...

- [2025-09-18]丹麦格耶KX-327RF低温车规晶振的卓越...

销售代表

销售代表