如何巧妙设计削顶正玄波至CMOS的转换电路?

来源:http://www.yijindz.com 作者:亿金电子 2020年06月16

如何巧妙设计削顶正玄波至CMOS的转换电路?

其实从一定意义上来说,想要设计晶振产品的输出逻辑由削顶正玄波转向CMOS的转换电路是非常简单的,只是通常情况下很少有人会注意到这样的问题,哪怕注意到了,这样的念头也只是昙花一现.那么削顶正弦波向CMOS转换的电路到底需要怎样设计呢? 我们这里讨论的削顶正玄波以及CMOS都是指有源晶振的输出逻辑,说到石英晶体振荡器的输出逻辑我们不得不来盘一下它了,因为可能会有很多朋友对此知之甚少,晶振的输出逻辑种类繁多,下面我们一一介绍

1)TTL:Transistor-Transistor Logic(晶体管-晶体管逻辑电路),传输延迟时间快、功耗高,属于电流控制器件.

2)CMOS:Complementary Metal Oxide Semiconductor(互补金属氧化物半导体CMOS逻辑电路),传输延迟时间慢、功耗低,属于电压控制器件.

3)ECL:Emitter-CoupleLogic(发射极耦合逻辑电路),该电路的特点是基本门电路工作在非饱和状态.ECL电路具有相当高的速度,平均延迟时间可达几个毫微秒甚至亚毫微秒数量级.ECL电路的逻辑摆幅较小(仅约0.8V,而TTL的逻辑摆幅约为2.0V),当电路从一种状态过渡到另一种状态时,对寄生电容的充放电时间将减少,这是ECL电路具有高开关速度的重要原因.但ECL输出的逻辑摆幅小,对抗干扰能力不利.另外ECL电路具有很高的输入阻抗和低的输出阻抗.

4)PECL:PosiTIve Emitter-Couple Logic(正发射极耦合逻辑电路).ECL电路速度快,驱动能力强,噪声小,很容易达到几百MHz的应用,但是功耗大,需要负电源.

5)LVDS:Low-Voltage DifferenTIal Signaling(低电压差分信号),为差分对输入输出,内部有一个恒流源3.5~4mA,在差分线上改变方向和电平来表示”1”和”0”.通过外部的100欧匹配电阻(并接在差分线上靠近接收端)转换为±350mV的差分电平.

6)Clipped Sine Wave:削顶正弦波(Clipped Sine Wave).相比方波的谐波分量少很多,但驱动能力较弱,在负载10K//10PF时Vp-p为0.8Vmin.通常为SMD7050、SMD5032、3225贴片晶振等封装的表贴温补晶振使用的输出波形.

7)SinWave:通常晶振正弦波输出的负载阻抗为50欧姆.波形的谐波分量很小,一般谐波抑制都优于-30dBc.正弦波输出晶振通常用于射频信号处理、频率源等应用场合.

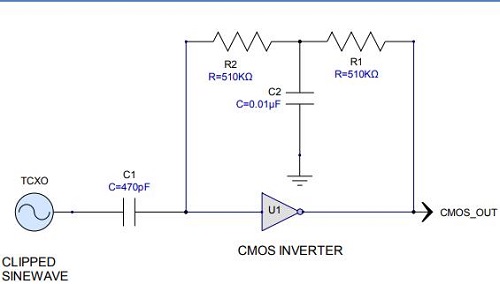

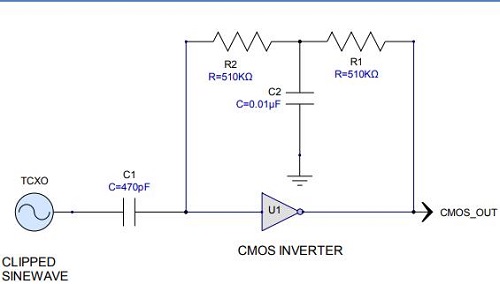

可见削顶正弦波与CMOS属于不同类别的输出方式的,具体的转换电路如下图所示.

上述电路将削波的正弦波波形转换为CMOS波形.CMOS反相器选择必须针对工作频率进行额定.正确选择逆变器,该电路可以在高达100MHz的频率下工作.

上述电路将削波的正弦波波形转换为CMOS波形.CMOS反相器选择必须针对工作频率进行额定.正确选择逆变器,该电路可以在高达100MHz的频率下工作.

但是还存在一定的缺陷,特别是对于温补晶振来说影响会比较大,由于该电路与CMOS反相器的输出隔离,因此它给TCXO带来了恒定的负载.由R1,R2和C2组成的反馈网络可以用一个1Meg欧姆的电阻代替,但是TCXO将被CMOS反相器的输出跳变拉动.

其实从一定意义上来说,想要设计晶振产品的输出逻辑由削顶正玄波转向CMOS的转换电路是非常简单的,只是通常情况下很少有人会注意到这样的问题,哪怕注意到了,这样的念头也只是昙花一现.那么削顶正弦波向CMOS转换的电路到底需要怎样设计呢? 我们这里讨论的削顶正玄波以及CMOS都是指有源晶振的输出逻辑,说到石英晶体振荡器的输出逻辑我们不得不来盘一下它了,因为可能会有很多朋友对此知之甚少,晶振的输出逻辑种类繁多,下面我们一一介绍

1)TTL:Transistor-Transistor Logic(晶体管-晶体管逻辑电路),传输延迟时间快、功耗高,属于电流控制器件.

2)CMOS:Complementary Metal Oxide Semiconductor(互补金属氧化物半导体CMOS逻辑电路),传输延迟时间慢、功耗低,属于电压控制器件.

3)ECL:Emitter-CoupleLogic(发射极耦合逻辑电路),该电路的特点是基本门电路工作在非饱和状态.ECL电路具有相当高的速度,平均延迟时间可达几个毫微秒甚至亚毫微秒数量级.ECL电路的逻辑摆幅较小(仅约0.8V,而TTL的逻辑摆幅约为2.0V),当电路从一种状态过渡到另一种状态时,对寄生电容的充放电时间将减少,这是ECL电路具有高开关速度的重要原因.但ECL输出的逻辑摆幅小,对抗干扰能力不利.另外ECL电路具有很高的输入阻抗和低的输出阻抗.

4)PECL:PosiTIve Emitter-Couple Logic(正发射极耦合逻辑电路).ECL电路速度快,驱动能力强,噪声小,很容易达到几百MHz的应用,但是功耗大,需要负电源.

5)LVDS:Low-Voltage DifferenTIal Signaling(低电压差分信号),为差分对输入输出,内部有一个恒流源3.5~4mA,在差分线上改变方向和电平来表示”1”和”0”.通过外部的100欧匹配电阻(并接在差分线上靠近接收端)转换为±350mV的差分电平.

6)Clipped Sine Wave:削顶正弦波(Clipped Sine Wave).相比方波的谐波分量少很多,但驱动能力较弱,在负载10K//10PF时Vp-p为0.8Vmin.通常为SMD7050、SMD5032、3225贴片晶振等封装的表贴温补晶振使用的输出波形.

7)SinWave:通常晶振正弦波输出的负载阻抗为50欧姆.波形的谐波分量很小,一般谐波抑制都优于-30dBc.正弦波输出晶振通常用于射频信号处理、频率源等应用场合.

可见削顶正弦波与CMOS属于不同类别的输出方式的,具体的转换电路如下图所示.

但是还存在一定的缺陷,特别是对于温补晶振来说影响会比较大,由于该电路与CMOS反相器的输出隔离,因此它给TCXO带来了恒定的负载.由R1,R2和C2组成的反馈网络可以用一个1Meg欧姆的电阻代替,但是TCXO将被CMOS反相器的输出跳变拉动.

正在载入评论数据...

相关资讯

- [2024-11-09]温度补偿晶体振荡器 JT21LE,功耗极低...

- [2023-06-26]Rakon推出RakonXpress品牌的现成频率...

- [2023-06-20]Cardinal晶振公司环境政策,CSM1Z-A0B...

- [2023-06-20]Cardinal晶振ROSH证明,CX532Z-A2B3C5...

- [2023-06-17]为什么选择ClearClock有源晶振,AK2AD...

- [2021-01-21]低功耗性能且含数字温度补偿的时钟IC...

- [2020-12-04]TXC晶振车规级频率组件最新产品应用方...

- [2020-10-19]石英振荡器系列六——产品未来应用市...

销售代表

销售代表