在PCB板上,无源晶振如何置换成有源晶振

来源:http://www.yijindz.com 作者:亿金电子 2022年02月26

相信很多的工程的朋友和研发爱好者都会有这样的问题吧。无源晶振可以替换有源晶振吗?如果有又该如何操作呢?

首先我们要了解,有源和无源的区别

无源晶振

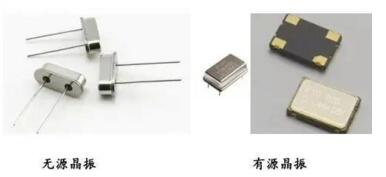

无源晶振也称为晶体谐振器,晶体谐振器通常以2脚跟4脚居多,无源晶振在电路中需要助外部电路起振,自身无法起振。无源晶振一般都是接入两个脚。

只有两个功能脚位且不具备方向性,无需担忧接反。单片机内部具备振荡电路结构,但仍需要在两端(时钟信号输出脚和时钟信号输入脚)连接一个无源晶振和两个与晶振负载电容(CL)匹配的外接电容(对地电容)才能组建成一套完整的时钟电路。在该电路中,无源晶振自身无法起振。

有源晶振

有源晶振是由石英晶振加震荡片组成的,也称晶体振荡器,已经内置IC,自身形成一套完整的振荡电路,施加所需额定电压。有源晶振不需要DSP的内部振荡器,信号质量好,比较稳定,而且连接方式相对简单。

有源晶振一般有4个脚,有个圆点标记的为1脚(空脚位),按逆时针(管脚向下)分别为2、3、4。有源晶振通常的用法:一脚悬空,二脚接地,三脚接输出,四脚接电压输入。

有源晶振引脚具备方向性,一定要找对电压输入脚,贴反极易导致有源晶振内部金属引线遭受强电流而熔断,造成有源晶振被烧毁而停振。

有源晶振引脚具备方向性,一定要找对电压输入脚,贴反极易导致有源晶振内部金属引线遭受强电流而熔断,造成有源晶振被烧毁而停振。

相对于无源晶体,有源晶振的缺陷是其信号电平是固定的,需要选择好合适输出电平,灵活性较差,而且价格高。

对于时序要求敏感的应用,个人认为还是有源的晶振好,因为可以选用比较精密的晶振,甚至是高档的温度补偿晶振。

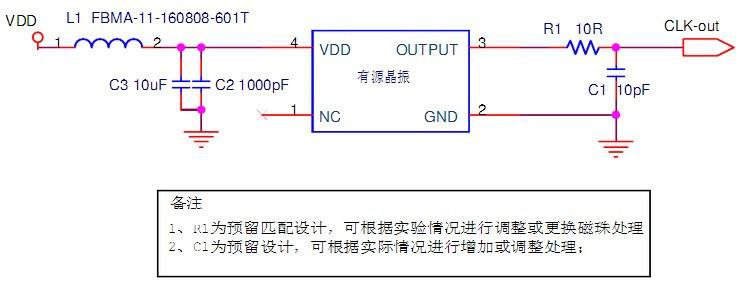

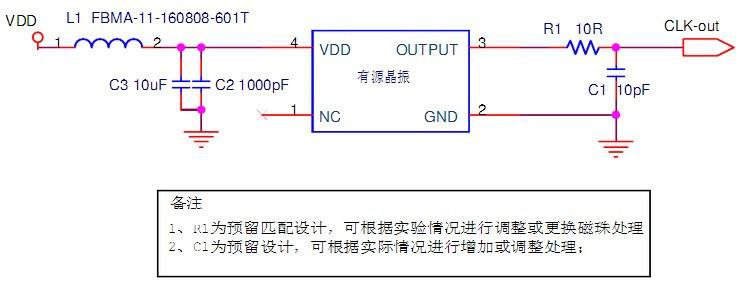

因此,有源晶振不能在原有电路中直接代替无源晶振。从技术上讲,若使用有源晶振代替无源晶振,我们需要对晶振电路进行修改,具体操作是:绕开原有无源晶振振荡电路,为有源晶振单独提供所需标称电压(VCC),将信号输出脚位(OUT)接至原有无源晶振信号输出端。

几点注意事项:

1、需要倍频的DSP需要配置好PLL周边配置电路,主要是隔离和滤波;

2、20MHz以下的晶体晶振基本上都是基频的器件,稳定度好,20MHz以上的大多是谐波的(如3次谐波、5次谐波等等),稳定度差;

因此强烈建议使用低频的器件,毕竟倍频用的PLL电路需要的周边配置主要是电容、电阻、电感,其稳定度和价格方面远远好于晶体晶振器件;

3、时钟信号走线长度尽可能短,线宽尽可能大,与其它印制线间距尽可能大,紧靠器件布局布线,必要时可以走内层,以及用地线包围;

4、通过背板从外部引入时钟信号时有特殊的设计要求,需要详细参考相关的资料。

此外还要做一些说明:

总体来说晶振的稳定度等方面好于晶体,尤其是精密测量等领域,绝大多数用的都是高档的晶振,这样就可以把各种补偿技术集成在一起,减少了设计的复杂性。

试想,如果采用晶体,然后自己设计波形整形、抗干扰、温度补偿,那样的话设计的复杂性将是什么样的呢?我们这里设计射频电路等对时钟要求高的场合,就是采用高精度温补晶振的,工业级的要好几百元一个。

特殊领域的应用如果找不到合适的晶振,也就是说设计的复杂性超出了市场上成品晶振水平,就必须自己设计了,这种情况下就要选用晶体了,不过这些晶体肯定不是市场上的普通晶体,而是特殊的高端晶体,如红宝石晶体等等。

无源晶振

无源晶振也称为晶体谐振器,晶体谐振器通常以2脚跟4脚居多,无源晶振在电路中需要助外部电路起振,自身无法起振。无源晶振一般都是接入两个脚。

只有两个功能脚位且不具备方向性,无需担忧接反。单片机内部具备振荡电路结构,但仍需要在两端(时钟信号输出脚和时钟信号输入脚)连接一个无源晶振和两个与晶振负载电容(CL)匹配的外接电容(对地电容)才能组建成一套完整的时钟电路。在该电路中,无源晶振自身无法起振。

有源晶振

有源晶振是由石英晶振加震荡片组成的,也称晶体振荡器,已经内置IC,自身形成一套完整的振荡电路,施加所需额定电压。有源晶振不需要DSP的内部振荡器,信号质量好,比较稳定,而且连接方式相对简单。

有源晶振一般有4个脚,有个圆点标记的为1脚(空脚位),按逆时针(管脚向下)分别为2、3、4。有源晶振通常的用法:一脚悬空,二脚接地,三脚接输出,四脚接电压输入。

相对于无源晶体,有源晶振的缺陷是其信号电平是固定的,需要选择好合适输出电平,灵活性较差,而且价格高。

对于时序要求敏感的应用,个人认为还是有源的晶振好,因为可以选用比较精密的晶振,甚至是高档的温度补偿晶振。

因此,有源晶振不能在原有电路中直接代替无源晶振。从技术上讲,若使用有源晶振代替无源晶振,我们需要对晶振电路进行修改,具体操作是:绕开原有无源晶振振荡电路,为有源晶振单独提供所需标称电压(VCC),将信号输出脚位(OUT)接至原有无源晶振信号输出端。

几点注意事项:

1、需要倍频的DSP需要配置好PLL周边配置电路,主要是隔离和滤波;

2、20MHz以下的晶体晶振基本上都是基频的器件,稳定度好,20MHz以上的大多是谐波的(如3次谐波、5次谐波等等),稳定度差;

因此强烈建议使用低频的器件,毕竟倍频用的PLL电路需要的周边配置主要是电容、电阻、电感,其稳定度和价格方面远远好于晶体晶振器件;

3、时钟信号走线长度尽可能短,线宽尽可能大,与其它印制线间距尽可能大,紧靠器件布局布线,必要时可以走内层,以及用地线包围;

4、通过背板从外部引入时钟信号时有特殊的设计要求,需要详细参考相关的资料。

此外还要做一些说明:

总体来说晶振的稳定度等方面好于晶体,尤其是精密测量等领域,绝大多数用的都是高档的晶振,这样就可以把各种补偿技术集成在一起,减少了设计的复杂性。

试想,如果采用晶体,然后自己设计波形整形、抗干扰、温度补偿,那样的话设计的复杂性将是什么样的呢?我们这里设计射频电路等对时钟要求高的场合,就是采用高精度温补晶振的,工业级的要好几百元一个。

特殊领域的应用如果找不到合适的晶振,也就是说设计的复杂性超出了市场上成品晶振水平,就必须自己设计了,这种情况下就要选用晶体了,不过这些晶体肯定不是市场上的普通晶体,而是特殊的高端晶体,如红宝石晶体等等。

正在载入评论数据...

相关资讯

- [2026-02-04]Skyworks赋能Nest视频门铃开启智能家...

- [2026-02-02]瑞萨第四代R-Car汽车芯片应运而生掀起...

- [2026-01-28]电子行业新突破IQD可变供电式振荡器震...

- [2026-01-24]5G与智能时代的幕后英雄Greenray精密...

- [2026-01-21]Skyworks电子展大放送栅极驱动器与Ga...

- [2025-10-24]光刻赋能NDK晶振开启800G/1.6T光通信...

- [2025-10-18]解锁液体检测新境界美国微芯MTCH9010...

- [2025-09-18]丹麦格耶KX-327RF低温车规晶振的卓越...

销售代表

销售代表